## 2. SYNTHESE DE FREQUENCE A PLL

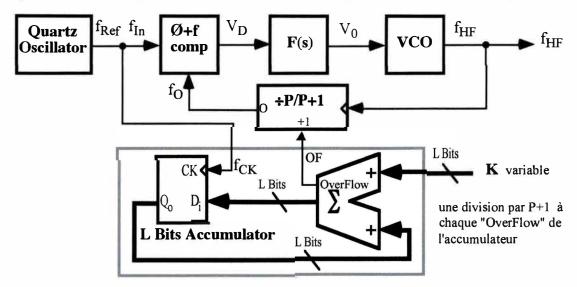

Avec une boucle PLL à diviseur fractionnaire, on veut effectuer une synthèse de fréquence agile couvrant une gamme de 861 MHz à 875 MHz par pas de 1 kHz ou plus petits.

Donner la relation f<sub>HF</sub> en fonction de f<sub>Ref</sub>, P, K et L lorsque la PLL est verrouillée et stabilisée.

La féquence de travail maximum de l'accumulateur et du comparateur de phase est limitée à  $f_{logic,max} = 30 \text{ MHz}$ .

On a le choix entre trois "Dual Modulus Prescaler": a) P = 16, b) P = 32 et c) P = 64. Seul le prescaler b) convient à cette application. Justifier ce choix et dire pourquoi a), respectivement c), ne conviennent pas (justifications avec valeurs numériques).

b)

$$\frac{875 \text{ TIHz}}{32} = 27.3 \text{ MHz}$$

$\angle$  [logic wax OK]  $\frac{33}{32} = 1.031 > \frac{875}{861} = 1.0163$   $\nu$

Avec le prescaler P = 32, déteminer la plage de fréquence  $f_{Ref,min}$   $f_{Ref,max}$  tolérable pour le quartz,

$$f_{Ref, max} = \frac{875 \, \Pi Hz}{33} = 26.515 \, MHz \, V$$

$$f_{Ref, max} = \frac{861 \, \Pi Hz}{32} = 26.906 \, MHz \, V$$

et le nombre minimum de bits L<sub>min</sub> nécessaire pour l'accumulateur.

Avec P = 32, L = 20 et  $f_{Ref} = 26.800$  MHz  $\pm 1$  ppm, déterminer la plage de fréquence totale que ce synthétiseur peut couvrir et sa résolution effective.

$$F_{HF} = 26.800 \text{ } \Pi \text{ } Hz \text{ } \left( 32 + \frac{K}{2^{20}} \right) \Rightarrow 857.6 \text{ } \Pi \text{ } Hz \text{ } K = (2^{20}-1) \Rightarrow 884.4 \text{ } \Pi \text{ } Hz \text{ } L = (2^{20}-1) \Rightarrow 884.4 \text{ } L = (2^{2$$

Quel est l'incrément  $\Delta K$  à imposer pour passer d'un cannal au suivant, sachant qu'ils sont espacés de 25 kHz ?

$$\Delta 1 < = Int \left( \frac{25000}{25.55847} \right) = 978$$

Quelles sont les deux principales sources d'imprécision de la fréquence absolue générée (estimations chiffrées)?

Le comparateur de phase-fréquence logique avec  $K_D = 5/4\pi \text{ V/rad}$

Le VCO est spécifié linéaire entre:

$$f_{HF} = 850 \text{ MHz} \text{ à } V_0 = 1 \text{ V}$$

et  $f_{HF} = 890 \text{ MHz} \text{ à } V_0 = 5 \text{ V}$

Dimensionner le filtre intégrateur de degré 1 permettant d'obtenir un temps d'établissement de la boucle  $t_s$  d'environ 100  $\mu$ s, avec un amortissement optimal  $\xi = 1$ .

$$K_{VCO} = \frac{40 \text{ MHz}}{L \text{ V}} \cdot 2M = 62.8 \text{ M rod /s V}$$

$$K_{O} = \frac{K_{VCO}}{32.5} = 1.93 \text{ M rod /s V}$$

$$K_{O}K_{D} = 769 \cdot 10^{3}$$

$$W_{O}K_{D} = 769 \cdot 10^{3}$$

$$W_{O}K_{D} = 769 \cdot 10^{3}$$

$$W_{O}K_{D} = 60'000 \text{ rod /s}$$

$$W_{O}K_{D} = \frac{6}{10^{-4}} = 60'000 \text{ rod /s}$$

$$\tau_2 = \frac{1}{\sqrt{\sqrt{Q}}} = \frac{33 \mu s}{2}$$